# Using the CORE-V MCU FPGA Platform

Hugh Pollitt-Smith, CMC Microsystems

SEPTEMBER 15, 2020 | OSDFORUM

# Agenda

- > About CMC Microsystems

- > Architecture of the CORE-V MCU FPGA Platform

- > CORE-V MCU FPGA Platform Development Environment

- > CORE-V MCU FPGA Platform setup

- > Demo: Building and Running an Application

- > Next steps

# Canada's National Design Network®

A Canada-wide collaboration between 67 universities/colleges to connect 10,000 academic participants with 1,000 companies to design, make and test micro-nanosystem prototypes.

#### 2019-20 Outcomes

3 460 publications

170 awards

85 patents awarded

450 collaborations with

industry

10 new startups

625 trained HQP moved to industry

#### Annually

1 275 connected professors

8 350 researchers

6 575 users of computer

aided design tools

200 physical prototypes

75 equipment rental items otherwise unaffordable to users

# Lowering barriers to technology adoption

State-of-the-art environments for successful design

- Selection of high-performance Computer Aided Design (CAD) tools and design environments

- Available via desktop or through CMC Cloud

- User guides, application notes, training materials and courses

CMC.ca/CAD

Services for making working prototypes

- Multi-project wafer services with affordable access to foundries worldwide

- Fabrication and travel assistance to prototype at a university-based lab

- Value-added packaging and assembly services

- In-house expertise for first-time-right prototypes

CMC.ca/FAB

Device validation to system demonstration

- Access to platform-based microsystems design and prototyping environments

- Access to test equipment on loan

- Access to contract engineering services

CMC.ca/LAB

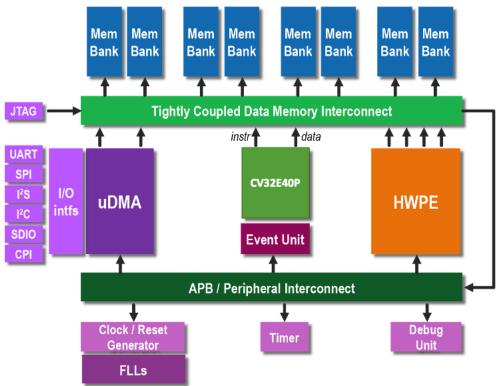

# Architecture of the CORE-V MCU FPGA

# PULPissimo/CORE-V MCU

# core-v-mcu repo directories

- doc

- fpga

- README.md

- cv32e40p\_bitstreams

- cv32e40p\_modified\_files

- pulpissimo

- pulpissimo\_nexys

- ips

- rtl

- sim

# core-v-mcu/ips/

```

adv dbg if

apb

apb interrupt cntrl

axi

common cells

cv32e4\overline{0}p

fpnew

fpu div sqrt mvp

generic FLL

hwpe ctrl

hwpe mac engine

hwpe-stream

jtag pulp

L2 tcdm hybrid interco

pulp_soc

riscv -> cv32e40p

riscv dbg

SCM

tbtools

tech cells generic

timer unit

udma

```

#### **Documentation**

#### CV32E40P:

https://core-v-docs-verif-strat.readthedocs.io/projects/cv32e40p\_um/en/latest/

### PULPissimo/CORE-V MCU:

https://github.com/openhwgroup/core-v-mcu/blob/master/doc/datasheet/datasheet.pdf

# core-v-mcu FPGA Development Environment

## Design Environment

- Ubuntu 18.04

- Xilinx Vivado (2019.2) WebPack is sufficient for NexysA7

- Mentor Graphics Questasim

- CORE-V GCC toolchain

- PULP-runtime

- PULP-SDK

- OpenOCD

# CORE-V MCU FPGA Platform Setup

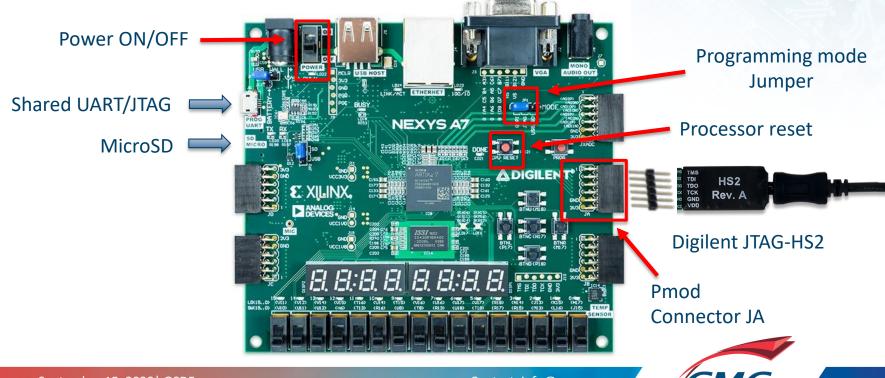

# Digilent NexysA7-100T FPGA Board

# Demo: Running an application

https://github.com/openhwgroup/core-v-mcu/blob/master/fpga/cv32e40p modified files/cv32e40p sort.tar.gz

# CORE-V MCU project https://github.com/openhwgroup/core-v-mcu/

fpga subfolder contains detailed instructions to:

- Install the CORE-V MCU environment

- Install and modify PULPissimo to instantiate CV32E40P and build the FPGA bitstream

- Download a pre-built FPGA bitstream

- Build and run an application on CV32E40P

# Next steps

# Get involved, contribute

- Use the platform, provide feedback, raise issues

- Enhance the architecture

- Integrate board peripherals, develop device drivers

- Demonstrate new tools (HW, SW, OS) in the environment

- Develop the runtime, SDK

- Develop applications and demos